# OPEN ETHERNET NETWORKING FOR MODERN AI/ML WORKLOADS

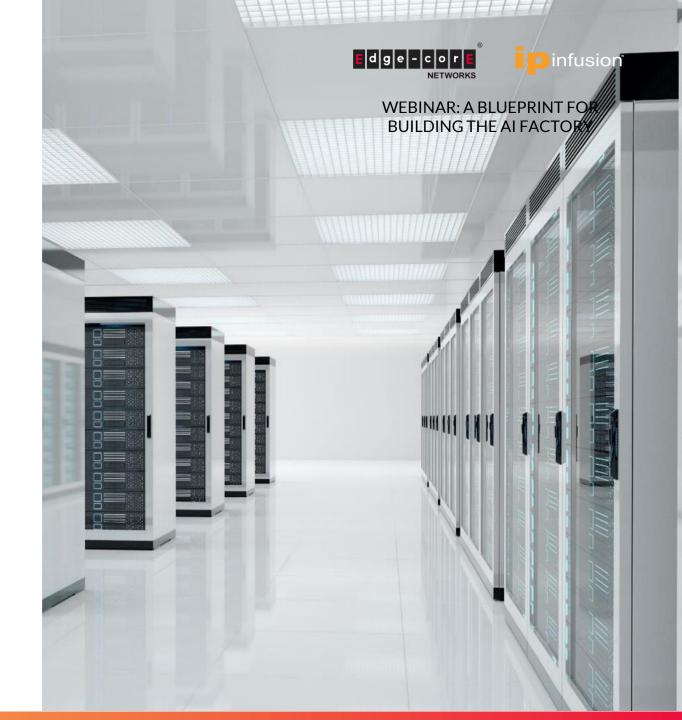

A BLUEPRINT FOR BUILDING THE AI FACTORY

ALAN HUANG Senior Product Manager

SUJAY GUPTA

Senior Solutions Manager

SEPTEMBER 10, 2025 | 14:00 AM BST | 6:00 AM PT

## **Table of Contents**

- Company Introductions

- Al Solution Ecosystem

- Hardware

- Software

- Use Case Deep Dive Ethernet Fabric for AI

- Ethernet vs InfiniBand Brief

- Summary and Future Development

- Q&A

ALAN HUANG

Senior Product Manager

ipinfusion\*\*

SUJAY GUPTA Senior Solutions Manager

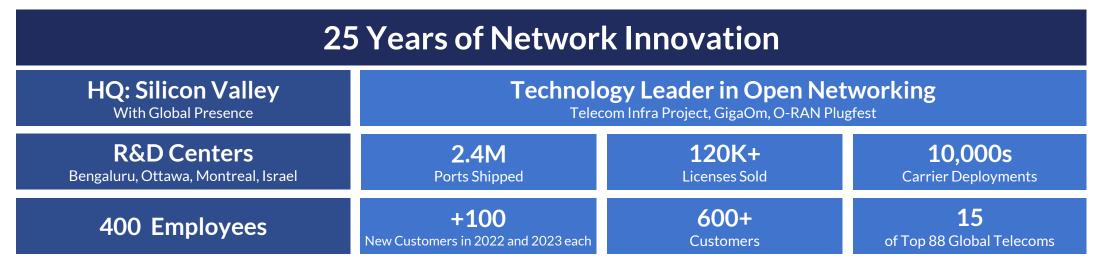

## **IP Infusion Corporate Overview**

#### **Product and Technology Leadership**

### **Total Network Disaggregation**

# IP Infusion Advantages for Open Networking

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

Most Comprehensive Open NOS

The Widest HW Solution Ecosystem

Open Optics Ecosystem

Centralized Monitoring and Management

24/7 Professional Support

**600+**Modern Networking Features

**40+**Supported Hardware Platforms

**100+**Qualified Optical Transceivers

## **IP Infusion Client Roster**

#### **NETWORK OPERATORS**

#### **NETWORK EQUIPMENT MANUFACTURERS**

## **About Edgecore**

Portfolio of Open Networking Products, Solutions and Services

Delivering to Large Tier1's and Enterprise **Customers Worldwide**

**Independent Branded Company** Accton Owned Subsidiary Since 2010

Worldwide Sales and Support, Headquartered in Hsinchu Taiwan

Flexible Business Model Solutions Provider

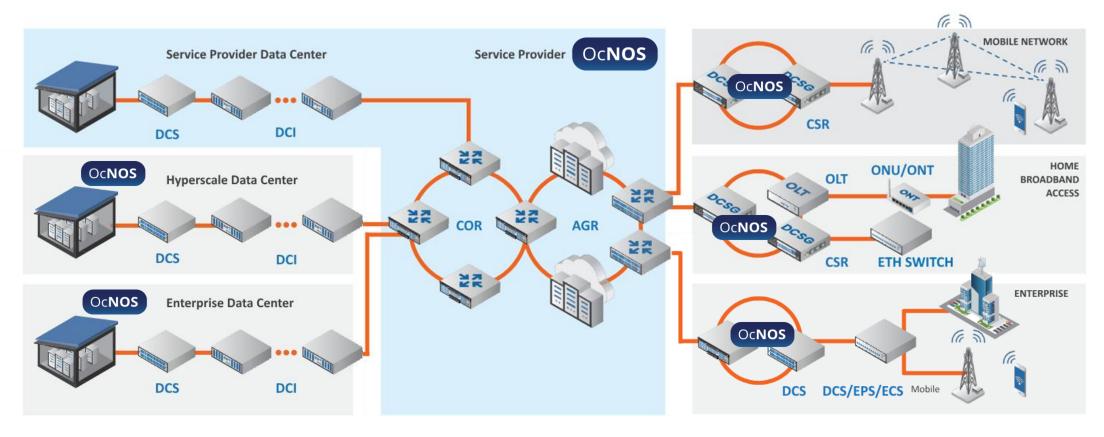

Oc**NOS**

**Telecom**

AI & Data Center Enterprise

**NOS Software**

# **About Accton:**The Parent Company of Edgecore

With over 35 years of experience, Accton is a well-known technology ODM/JDM provider for global enterprises, recognized for <u>innovative technologies</u> and <u>manufacturing excellence</u>, earning a distinguished industry reputation.

- Established in 1988

- Global operating sites extend across North America, Europe, and Asia

- Number of Employees: 6,500

- 2024 Revenue: USD3.4 billion

Manufacturing in **China** Space: 71,040 m<sup>2</sup>

Manufacturing in Zhunan, Taiwan Space: 15,518 m<sup>2</sup>

Manufacturing in **Vietnam** Space: 11,340 m<sup>2</sup>

Office and Warehouse in the United States

Brand new facility launched in 2024, in Zhubei, Taiwan

## Open Networking Solutions from Edge to Core

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

AI/Cloud Data Center Solutions

Service Providers

Solutions

**Enterprise Solutions**

## **Edgecore Data Center Portfolio**

IP Infusion OcNOS Qualified

2022

More than 50% of DC switches in 2<sup>nd</sup> largest marketplace

2025

World's largest Payment Gateway DC using Edgecore

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

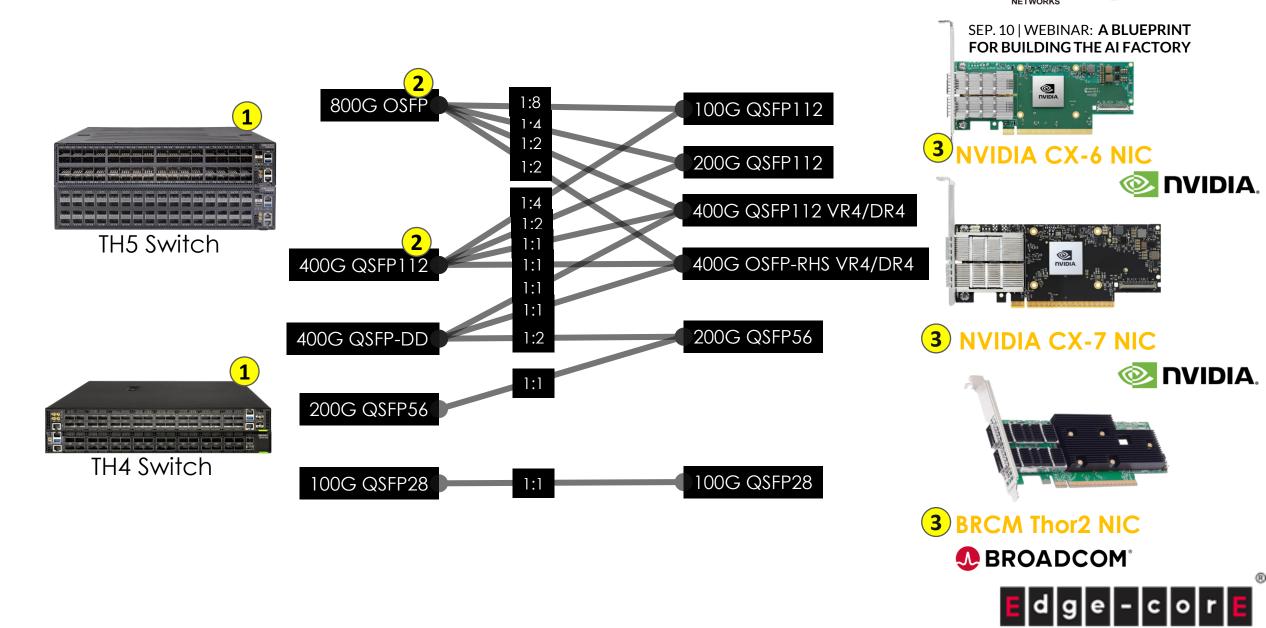

Spine Switches Tomahawk family

DCS511

32x 400G - TD4 - 12.8T

DCS510

32x 400G - TH3 - 12.8T

DCS520 64x 400G - TH4 - 25.6T

Leaf Switches Trident family

DC Mgmt/ Enterprise Switches Trident family

48x 1G, 4x 25G - TD3 - 480G

EPS121

48x1G, 6x10G - TD3-X2 - 108G

**EPS122** 48x1G(POE), 6x10G - TD3-X2

Al DC – a. High Radix b. Suits Leaf and Spine c. Low Latency d. E-W traffic

Qualified with IP Infusion

Enterprise/Cloud DC – a. 25/100/400G b. Over-Sub c. E-W and N-S traffic

Edge-corE

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

IP Infusion OcNOS Qualified - by Use Case

#### **Trident Family**

- Higher Buffer than Tomahawk

- Better QOS

- Feature Rich(Virtualization, IP)

AS5835-54T | DCS202 6x 100G, 48x 10G - TD3 - 1.08T

AS7816-64X | DCS500 64x 100G - TH2 - 6.4T

AS7726-32X | DCS204 32x 100G - TD3 - 6.4T

AS9736-64D | DCS520 64x 400G - TH4 - 25.6T

AS9726-32DB | DCS511

32x 400G - TD4 - 12.8T

AS9817-64D AIS800-640/D

64x 800G - TH5 - 51.2T

AS4625-54T | EPS121 **48x1G**, **6x10G** - TD3-X2 - 108G

AS5835-54X | DCS201 6x 100G, 48x 10G - TD3 - 1.08T

AS9716-32D | DCS510 32x 400G - TH3 - 12.8T

128 Gbps 1.08 - 2.0 Tbps

3.2 – 6.4 Tbps

12.8 - 25.6 Tbps

51.2 Tbps

Al Fabric Switch

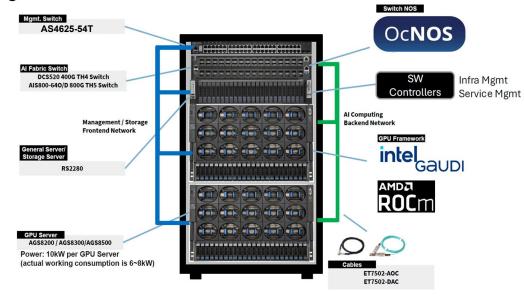

## **Edgecore Al Solution**

Deployment proven, open standards-based disaggregated Networking OS providing high performance, extensive programmability, flexibility and interoperability

#### **Data Center Switches**

High performance, low latency switches for GPU interconnect and leaf/spine use cases, bringing advanced load balancing and congestion control features needed for the critical parts of your network

#### **Edgecore GPU Server Portfolio**

#### **GPU Servers (AGS Series)**

State-of-the-art GPU servers for AI, machine learning, and data analytics to accelerate your most demanding workloads Intel Gaudi 2, Gaudi 3 AMD MI 300, MI 325

#### **Edgecore Al Rack Total Solution**

#### **Transceivers and Cables**

Enhance your network's performance and reliability with our high-quality transceivers and network cables, designed for seamless connectivity and superior data transmission

# The Modern - Accelerated Compute Systems \*Public cloud hosted GaaS v

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

- Next phase in Evolution of Computer Systems

- Every new modern Server/Workstation now has compute accelerators to power today's modern applications

#### Types of AI customers

- Cloud service providers

- Colo providers

- Enterprises (various verticals: logistics, oil exploration, chemical, government, etc.)

#### \*Public cloud hosted GaaS vs on-prem AI DC cost comparison:

Average 3-Year Reserved H100 public cloud price: 8,000 GPUs 8000 \* \$3.00/hour \* 24 hours/day \* 365 days/year \* 3 years = \$631M

#### \*On-prem AI DC

1,000 H100 GPU servers (8 GPUs per server):

1,000 \* \$120K = \$120M

64 IP Infusion TH5 bundles + frontend-network/storage-fabric switches < \$3M

3Y power cost ~ \$37M (US industrial avg)

3Y TCO savings > 74%

Cloud Based GPU GPU Accelerated Data Analytics

Data scientists, researchers and developers

Multi-GPU Based Data Centers

Gives Data Locality, Model Training and Tuning Capabilities – Serves as the foundation for organizations in the Al maturity cycle Deployment

Platforms

which can

Infer at Real

Time

## Al Stack and Performance

**Application**

**Platform**

**Acceleration Libraries**

System Software

Example: CUDA/DOCA/Magnum IO/Base

Command/Forge

Hardware GPU's, CPU's, DPU's, NIC, Switch, Optics

## GPU's have different architectures for different workloads:

- Large Scale LLM Training and Inference NVIDIA B200, H100 AMD MI 300, MI 325 Intel Gaudi

- Data Analytics, Conversational AI, Language Processing

NVIDIA H100

- Gaming, 3D Rendering NVIDIA L405

- Machine Learning NVIDIA Grace

#### Nature of GPU workloads

- GPU's perform parallel processing, to maximize GPU efficiency the data must always be available. Which in turn requires High bandwidth with low latency and low jitter.

- As AI models and related datasets are growing, there is a need for multi-GPU systems.

- Certain AI models can be efficiently run on multi-GPU systems

## Multi-GPU Systems & Performance

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

- Overall performance of multi-GPU dependent on:

Data Must Always be Available for the GPU'

- Hardware

- Data Management

- ➤ GPU utilization

- Network Configuration

- GPU to GPU communication All to All PCIE not sufficient

- Chip-to-Chip Interconnect technologies such as ('Nvlink + NvSwitch', AMD Infinity Fabric, UA link)

#### **Multi GPU Systems**

- Scale-Up Has inherent Weak Fault Tolerance

- Scale-Out Has Robust Fault Tolerance

- Network Topology

- Bandwidth and Latency

- Network Protocols

- Data Transferring Techniques

- Management Methods

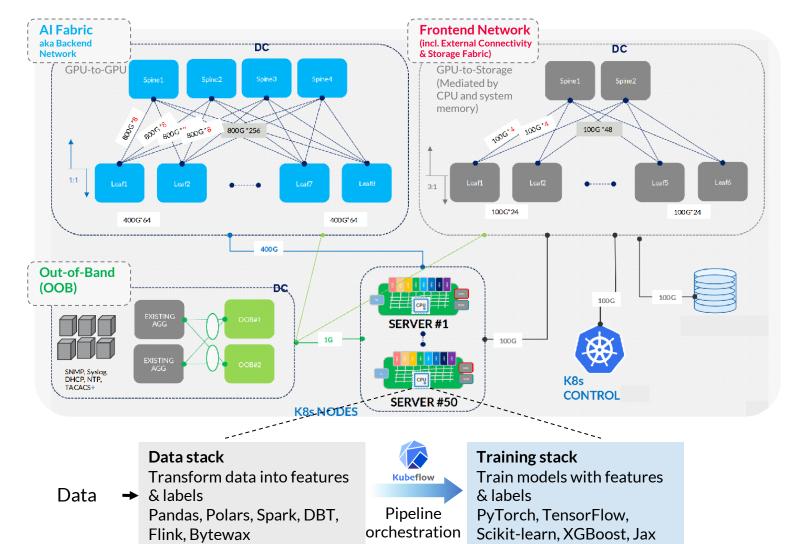

## OcNOS AI/ML Use Case Review

SEP. 10 | WEBINAR: **A BLUEPRINT FOR BUILDING THE AI FACTORY**

### **OcNOS Network Service Highlights**

Powering AI/ML data center network

#### Al Fabric (aka Backend Network)

- Ethernet based Layer 3 IP network

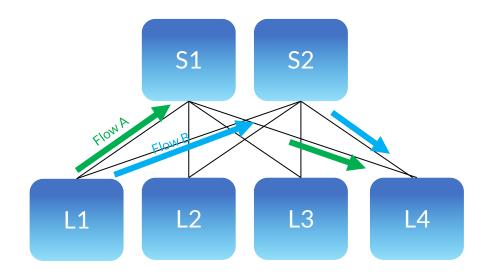

- Dynamic load balancing to avoid collision of long lasting elephant flows

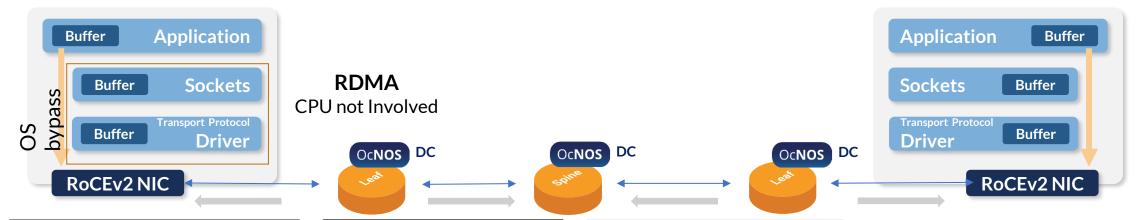

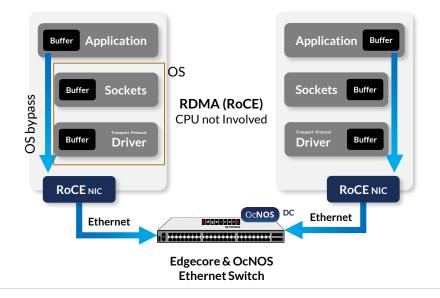

- •Lossless ROCEv2 (*RDMA over Converged Ethernet*) transport via PFC (*Priority Flow Control*) and ECN (*Explicit Congestion Notification*)

- Efficient support for mixed traffic types via ETS (*Enhanced Traffic Selection*)

## Frontend Network (incl. External Connectivity & Storage Fabric)

- EVPN-VxLAN overlay network

- Dynamic load balancing to avoid collision of long lasting elephant flows

- •Lossless ROCEv2 (*RDMA over Converged Ethernet*) transport via PFC (*Priority Flow Control*) and ECN (*Explicit Congestion Notification*)

- Efficient support for mixed traffic types via ETS

#### **Out-of-Band (OOB) Device Management**

- Layer 2 and layer 3 feature support

- Redundancy and availability

- Access control and security

# Scaling the Al Fabric – A Modular Approach

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

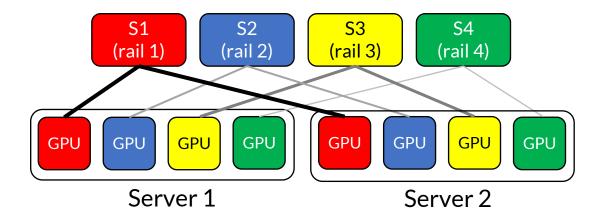

Rail Architecture - 32k GPU Example All switches are Tomahawk 5 8 RAILs 32 Spine PODs 8 RAILs OcNOS OCNOS OCNOS OCNOS OCNOS OCNOS 800G 64 Leaf PODs Oct DS OcNOS OcNOS OCNOS OCNOS OCNOS OCNOS Od OS OcNOS OCNOS OCNOS OCNOS Rail-as-a-separate-CLOS design 400G Each server's 8 GPUs is assigned to a 64 servers/512 specific rail 64 servers/512 **GPUs** Inter-GPU fabric on each server provides **GPUs** inter-rail GPU communication POD#1 POD#64 Rail 8 Rail 1 **Training** Layer 1-10 Layer 71-80 batches Al job x Scale-up GPU interconnect Benefits: number of switches is minimized (no super-spine and 5-stage CLOS), route scale Data passed to Data passed to next layer/rail is minimized next layer/rail

## Route Scale for 32K GPU AI Fabric

What each leaf and spine must hold

|               | Leaf                                                                                                        | Spine                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Advertises    | 64/32 local GPU IPs                                                                                         | Own loopback                                                                                                               |

| Receives      | 4,064 routes (from all other leaves of the same rail + loopbacks of spine peers)                            | <b>4,160 routes</b> (local GPU IPs on each of 64 leaf neighbors + loopbacks of leaf neighbor)                              |

| Adj-RIB-In    | 129,056 paths<br>(32-way ECMP per remote /32, single path for each spine peer loopback)                     | <b>4,160 paths</b> (single path per each leaf neighbor for its local GPU IPs, single path for each leaf neighbor loopback) |

| FIB           | 4,064 routes (one shared 32-way ECMP next-hop group comprised of spine peers reused by all remote prefixes) | 4,160 routes (single next-hop switch for each route)                                                                       |

| Re-advertises | None                                                                                                        | <b>4,160 / 32s</b> to 64 leaf neighbors                                                                                    |

Note: OcNOS supports BGP peer group, BGP graceful restart and HW based fast link failover to reduce BGP updates resulted from events like link failure and BGP control plane restart

# AI/ML Workload and Management/Control Traffic Types

| Traffic Type                             | Typical<br>Volume   | Frequency                        | Purpose                                                          | Characteristics                                       | Transport Fabric                                        |                               |

|------------------------------------------|---------------------|----------------------------------|------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------|-------------------------------|

| 1. Gradient Synchronization / All-Reduce | Very High           | Per step or iteration            | Sync model parameters                                            | Long-lived, high-<br>throughput,<br>latency sensitive | GPU <-> GPU                                             |                               |

| 2. Activation and<br>Feature Map<br>Data | Very High           | Per step or iteration            | Exchange intermediate tensors during model/ pipeline parallelism | Long-lived, high-<br>throughput,<br>latency sensitive | GPU <-> GPU                                             | ➤ Al Fabric                   |

| 3. Checkpointing                         | Moderate<br>to High | Periodic (every N minutes/steps) | Save model snapshots                                             | Large, bursty file transfers                          | CPU <-> storage                                         |                               |

| 4. Bulk I/O                              | Moderate<br>to High | Periodic (every N minutes/steps) | Load training data /<br>write results                            | Large-volume,<br>often parallel                       | CPU <-> storage                                         | Frontend                      |

| 5. Control<br>Messaging                  | Low                 | Continuous, small bursts         | Job coordination, sync                                           | Small packets, periodic or bursty                     | worker nodes <-><br>monitoring/ management<br>system(s) | Network/<br>Storage<br>Fabric |

| 6. Logs /<br>Telemetry                   | Very Low            | Steady or bursty                 | Record metrics or events                                         | Low rate, asynchronous                                | worker nodes <-><br>monitoring/ management<br>system(s) | Гарпс                         |

# QoS setting Example for Each AI/ML Traffic Type

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

Al Fabric ETS Setting

| Traffic Type | DSCP         | 802.1p PCP | Forwarding<br>Class | Queue Number            | Scheduling (within class)        | PFC<br>Enabled | ECN Enabled                  |

|--------------|--------------|------------|---------------------|-------------------------|----------------------------------|----------------|------------------------------|

| CNP          | 46 (EF)      | 5 or 7     | CNP-LOSSLESS        | 7 (Highest<br>Priority) | Strict Priority (SP)             | YES            | (N/A - source of ECN signal) |

| RoCEv2 Data  | 26<br>(AF31) | 3 or 4     | ROCE-<br>LOSSLESS   | 4 (High Priority)       | WRR / SP (if truly single class) | YES            | YES                          |

### Frontend Network/ Storage Fabric

**ETS Setting**

| Traffic Type                  | DSCP               | 802.1p PCP | Forwarding<br>Class | Queue Number   | Scheduling (within class) | PFC<br>Enabled | ECN Enabled                  |

|-------------------------------|--------------------|------------|---------------------|----------------|---------------------------|----------------|------------------------------|

| CNP                           | 46 (EF)            | 7          | CNP-LOSSLESS        | 7 (Higher SP)  | Strict Priority (SP)      | YES            | (N/A – source of ECN signal) |

| AI/ML Storage I/O<br>(RoCEv2) | 26<br>(AF31)       | 4          | STORAGE-<br>ROCE    | 4              | WRR (min bandwidth)       | YES            | YES                          |

| AI/ML<br>Management/Control   | 46 (EF)            | 5          | AI-CONTROL          | 5 (Highest SP) | Strict Priority (SP)      | NO             | YES                          |

| Logs / Telemetry              | 0<br>(Default<br>) | 0          | BEST-EFFORT         | 0              | WRR / DRR                 | NO             | YES                          |

# **Enabling Hop-by-Hop Lossless Transport via DCBX**

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

Leaf pushing PFC and ETS settings and application priority mapping to host via DCBX

#### PFC:

Which priorities have PFC enabled (e.g. priority 3)

#### ETS:

Priority-to-TC mapping, bandwidth allocation per TC

#### **Application Priority:**

Map UDP port to priority (e.g. request host to map  $RoCEv2 \rightarrow CoS 3$ )

Leaf pushing PFC and ETS settings to spine via DCBX

#### PFC:

Which priorities have PFC enabled (e.g. priority 3)

#### ETS:

Priority-to-TC mapping, bandwidth allocation per TC

Leaf pushing PFC and ETS settings to spine via DCBX

#### PFC:

Which priorities have PFC enabled (e.g. priority 3)

#### ETS:

Priority-to-TC mapping, bandwidth allocation per TC

Leaf pushing PFC and ETS settings and application priority mapping to host via DCBX

#### PFC:

Which priorities have PFC enabled (e.g. priority 3)

#### ETS:

Priority-to-TC mapping, bandwidth allocation per TC

#### **Application Priority:**

Map UDP port to priority (e.g. request host to map RoCEv2  $\rightarrow$  CoS 3)

DCBX ensures every switch and NIC along the path reserves consistent bandwidth and maps CoS values to queues the same way

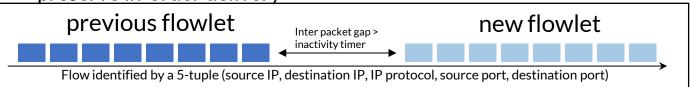

## **Dynamic Load Balancing (DLB)**

Traditional ECMP hash-based link selection is fixed throughout the flow even when port load and port queue size change

(destination prefix, packet hash) → output link/nexthop

DLB dynamically selects output member link in an ECMP group (i.e. group of next hops for a destination prefix) for a flow

(destination prefix, dynami $\hat{\mathbf{d}}$  index)  $\rightarrow$  output link/nexthop

Dynamically change based on the following conditions Link utilization

Queue depth / buffer pressure

Packet drops

LAG/ECMP member availability

• Change of output link for a flow only takes effect for new flowlet to preserve in-order delivery

Reactive Path Rebalancing (RPR) mode of DLB probabilistically reassigns a continuous incoming stream to a better quality (less loaded) egress member if quality is good by a configured delta

# Network Observability – Example Sensor Paths

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

#### Per leaf

| Metric category                        | Paths per interface | Interfaces                   | Total paths |

|----------------------------------------|---------------------|------------------------------|-------------|

| Interface counters                     | 1                   | 80 (64 downlinks+16 uplinks) | 80          |

| Optics metrics                         | 1                   | 80                           | 80          |

| Queue stats (per-queue)                | 8                   | 80                           | 640         |

| Buffer depth (per-port)                | 1                   | 80                           | 80          |

| BGP neighbor state (1 per uplink port) | 1                   | 16                           | 32          |

| Grand Total                            |                     |                              | 912 paths   |

### Per spine

| Metric category                 | Paths per interface       | Interfaces | Total paths |

|---------------------------------|---------------------------|------------|-------------|

| Interface counters              | 1                         | 32         | 32          |

| Optics metrics                  | 9 (1 module + 8 per-lane) | 32         | 288         |

| Queue stats (per-queue)         | 8                         | 32         | 256         |

| Buffer depth (per-queue)        | 8                         | 32         | 256         |

| BGP neighbor state (1 per port) | 1                         | 32         | 64          |

| Grand Total                     |                           |            | 896 paths   |

#### **Optional paths** (for more granularity)

- Per-lane optics metrics for media side (8 lanes/port) in addition to per-port module level optics metrics

- Per-queue buffer depth

- Optional per-lane optics can be enabled only on spines to monitor fiber links

- Although per-queue buffer depth monitoring is more critical on leaves, leaves already have many sensor paths

Real-time gNMI

**Telemetry**

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

- Reserve lossless queues per job

- Program/reprogram priorityto-traffic-class mapping and bandwidth per job

- Activate dynamic load balancing on job specific links

OcNOS Edgecore Al Fabric

Automation Platform

Al Job Orchestrator / Al Framework

| Rail | Link<br>Utilization | Buffer<br>Depth | Action                                                                        |

|------|---------------------|-----------------|-------------------------------------------------------------------------------|

| 1    | 90%                 | High            | Offload gradient aggregation to rail 2 GPUs temporarily                       |

| 2    | 30%                 | Low             | Additionally perform Layer 1's gradient aggregation temporarily               |

| 3    | 50%                 | Medium          | Normal scheduling                                                             |

| 4    | 10%                 | Low             | Start next micro-batch from rail 4 instead of rail 1 (i.e. rail 4 -> Layer 1) |

## **Driving GPU Efficiency with Efficient** Networking

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

#### **Key Design Considerations**

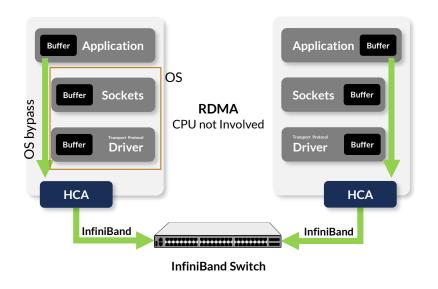

- Usage of RDMA High Bandwidth flows and Utilization

- Usage of Low Jitter Tolerance

- Design Network for Non-Blocking paths with High Bandwidth

- **Predictive Performance**

Single or few workloads ΑI Extremely Large Models **Factories**

One/Few users

Multi Tenant

Variety of Workloads

**Ethernet**

InfiniBand

Less complex jobs

AI Cloud

Increasing AI workloads and Large-Scale Gen AI training has shown standard Ethernet to be slow.

#### **ROCE (RDMA over Converged Ethernet)**

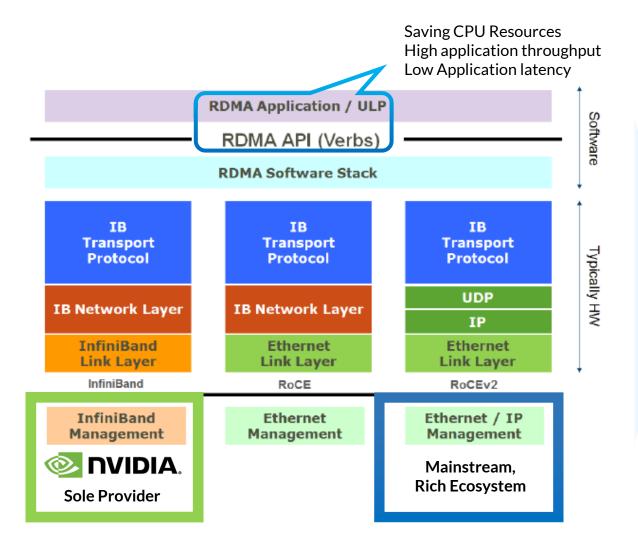

- ROCEv2 (RDMA over Converged Ethernet) uses IB packet header and encapsulates with UDP header

- Efficient data transfer where the OS is bypassed and enables fast access to remote data

- Supports message passing, sockets, and storage protocols

- Support by all major operating systems

- ROCE is an Open Source and a formal IBTA (Infiniband Trade Association) standard

## RDMA, RoCEv2 and UEC

UEC is enhancing RoCEv2 drawbacks and improve in many layers that ideal for mixing workloads

# Driving GPU Efficiency with Efficient Networking

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

| Dimension               | InfiniBand (IB)                                            | iWARP                                                                                   | RoCE v2                                                                                                                                      |

|-------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Specification / Release | IBTA Spec 1.0 (2000)                                       | IETF RDDP (2003)                                                                        | IBTA Annex 17 (2014)                                                                                                                         |

| Wire format             | Native IB frame                                            | IB frame carried in <b>TCP/IP</b>                                                       | IB frame carried in <b>UDP/IP</b> (UDP 4791) [RoCE v1 was L2 Hdr, with v2 it supports L3 is routeable with ECMP and DLB]                     |

| Layer reach             | Proprietary L1/L2 switched fabric                          | Routable Layer-3; crosses subnets                                                       | Routable Layer-3; crosses subnets                                                                                                            |

| Switching & control     | IB switches + Subnet Manager                               | Standard Ethernet/IP switching & routing; <b>no PFC</b> required                        | Lossless Ethernet switches with PFC                                                                                                          |

| Lossless guarantee      | Built-in credit-based flow control                         | No lossless fabric needed; TCP is reliable & in-order, tolerates loss/retransmit        | PFC                                                                                                                                          |

| Congestion control      | IB-CC (link-level credits)                                 | TCP window/ECN (Reno/CUBIC/DCTCP, etc.) — window-based                                  | DCQCN most common (Reactive CC w/ ECN)                                                                                                       |

| <b>CPU</b> involvement  | Near-zero copy RDMA; minimal CPU                           | Same as IB                                                                              | Same as IB                                                                                                                                   |

| Scalability limits      | Tens of thousands of nodes per fabric (topology-dependent) | Scales with IP routing—data-center or multi-DC                                          | Scales with IP routing—data-center or multi-DC                                                                                               |

| Typical deployments     | HPC supercomputers, AI clusters that value lowest latency  | -                                                                                       | Large Al clusters, cloud RDMA services, multi-site fabrics                                                                                   |

| Strengths               | Lowest latency, mature HPC software stack                  | <b>No PFC required</b> ; works on standard IP networks; resilient to loss/reorder (TCP) | L3 routeability, coexists with traditional IP, flexible                                                                                      |

| Weaknesses              | Requires dedicated hardware & management; higher CapEx     | Higher TCP/IP latency, small ecosystem                                                  | Adds UDP/IP overhead; still needs PFC/ECN tuning for true lossless ness [Go-Back N Retransmission – requires lossless and In-order delivery] |

Latency: IB<RoCEv2<i-WARP

## **UEC – Building Blocks**

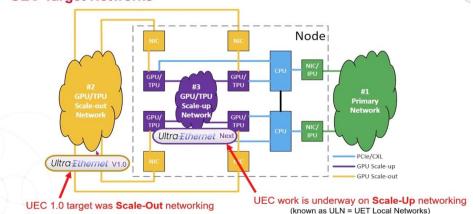

**AIFH** – Allows for smaller packet size required and sufficient for Fabric communication

**UR** – Mechanism to allow for link partners to request retransmission upon FEC failures

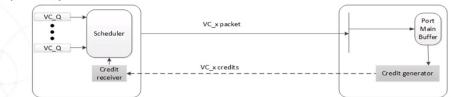

**CBFC** – Targets to provide link layer level lossless operations for VC

#### **Credit Based Flow Control**

- Targets to provide link-layer lossless operations for each lossless VC over links between two peer devices to enable lossless buffering in Rx devices.

- Virtual Channel represents parts of port traffic and can be flexibly configured as lossless or lossy

- At receiver end

- Pre-allocate for a port in Rx device headroom buffer space for lossless traffic

- Generate credit generation based on port buffer availability in receiver

- Advertise credits to Tx device

- CBFC Credit messages are used for transmission of credits from receiver to sender

- The sender keeps track of the available credits and its scheduler is allowed to schedule a VC queue only if it has credits

#### Al Fabric Header for Routed Flows

- · Reduced IPG (Inter-Packet Gap)

- 1B to 8B based on packet alignment (vs. Ethernet standard 12B)

- · Optimized Fabric Header: Fields [] Are Optional

|         | the state of the s |             |                     |                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|---------------------------|

| DA (6B) | SA (6B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | [VLAN (4B)] | AFH<br>Ethtype (2B) | [AFH_Extension (0B - 4B)] |

- Retains Ethernet-like structure for coexistence with IPv4/v6

- Minimize overhead for small packets by combining L2 (MAC) and L3 (IP) headers

- Addressing is overlaid on SA/DA, usable for single-tier (eg scale-up) and multi-tier (eg scale-out) fabrics

- Ethertype indicates the presence of a AFH\_Hdr or a standard header such as IPv4/v6

- VLAN tag is optional (eg for security)

- AFH\_Hdr includes fields commonly used for routing (hop count, traffic class, congestion, etc.)

- Allows for coexistence with standard IPv4/v6 packets and interop with standard MACs

- Supports ECN and other fabric notifications

- · AFH format is user-defined

- AFH Address space (# address bits) can be defined by system designer

- AFH EtherType determines AFH Extension Size, which can be 0, 2, 3, or 4 bytes

- TU can simultaneously support two different AFH formats with different AFH Ethertypes

NOTE: AFH was developed prior to UEC, and while AFH and the UEC's Unified Forwarding Header (UFH) have some similarities, they are distinct and not equivalent

#### **Link-Layer Retry Architecture**

#### LLR Scope

- LLR retransmits packets due to FEC/CRC errors on a full duplex Ethernet link

- Much faster recovery than end-to-end "TCP level" retransmission

- LLR does not protect against dropped packets due to buffer congestion

#### LLR Architecture

- Ethernet extensions:

- A sequence number is placed in each packet's preamble.

- Data receiver sends ACK/NACK messages (8B Control Ordered Set) for correctly or incorrectly received packets.

- MAC TX contains replay buffer to support retransmission upon receiving NACK.

- After receiving NACK, packet stream replays from lost or corrupted packet

- It is a Go-back-N packet-based protocol.

- Initialization Sequence

- Handshake between link partners to reset starting sequence numbers before sending traffic

SEP. 10 | WEBINAR: A BLUEPRINT

FOR BUILDING THE AI FACTORY

### Energy-efficient ASICs and optics reduce power per Gbps, aligning with green Data Center narrative

New Paradigm for Al Interconnect: Includes Features from Copper SerDes and Optical DSPs

- 800G DPO\$ to 800G LPO\$ = up to 50% saving

- Generic 800G 2xDR4 power consumption is 14.5W while 800G LPO is typical 7.5W, reflecting 48%+ saving

3

#### **Cut Down TCO: Electrical Cable for Short-Reach Connection**

- Direct Attach Copper (DAC)

- Active Electrical Cable (AEC)

ET7502-DAC-xM

|                   | 400G DR Optical<br>Transceiver | 400G AEC Cable | 400G DAC Cable |

|-------------------|--------------------------------|----------------|----------------|

| Max Length        | 500 meters                     | 7 meters       | 3 meters       |

| Power consumption | 10 watt                        | 5 watt         | 0.3 watt       |

Max length and power consumption for 400G connectivity

#### **Cut Down TCO: LPO Module + Fiber Cable**

- Linear-drive Pluggable Optics (LPO)

- · After eliminating some DSP modules

- Lower power consumption

- Lower latency

- Need tuning per model per port

|                   | 800G DR Optical Transceiver | 800G LPO Module         |  |

|-------------------|-----------------------------|-------------------------|--|

| Latency           | 50~70 nanosecond            | Less than 10 nanosecond |  |

| Power consumption | Typical 14.5 watt           | Typical 7.5 watt        |  |

Latency and power consumption for 800G connectivity

Incredibly Strong Industry Reception: 100+ Companies Worldwide

#### **UEC Target Networks**

Ultra **Ethernet**

# OcNOS AI/ML Solution Customer Benefits

SEP. 10 | WEBINAR: A BLUEPRINT FOR BUILDING THE AI FACTORY

AI/ML Networks with RDMA over InfiniBand

AI/ML Networks with RDMA over Converged Ethernet (RoCE)

Choose **Edgecore** and **OcNOS Ethernet Fabric** for you Al Cluster if you need:

### **Ubiquity and Interoperability**

Seamless integration with existing network infrastructure + modern Al networking stack

#### **Mature Open Ecosystem**

Widest and rapidly evolving ecosystem of compatible AI switches and optics with global support

### **Superior TCO**

Ready to deploy open networking solution with perpetual licensing, and leading support pricing

### **WEBINAR:**

**OPEN ETHERNET NETWORKING FOR MODERN** AI/ML WORKLOADS BUILDING THE AI FACTORY

**ALAN HUANG Senior Product Manager** infusion

**SUJAY GUPTA Senior Solutions Manager**

### **WEBINAR:**

OPEN ETHERNET NETWORKING FOR MODERN AI/ML WORKLOADS BUILDING THE AI FACTORY

# THANKYOU

www.ipinfusion.com

www.edge-core.com

## Switch - Optics - NIC

Edge-corE

**i**pinfusion™